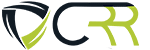

H2: 7475 4-Bit Bi-Stable Latch IC (DIP) Overview

The 7475 4-Bit Bi-Stable Latch IC is a TTL logic device that provides reliable temporary data storage for digital systems. It integrates four independent bistable latches in a single 14-pin Dual In-line Package (DIP), making it ideal for prototyping, buffering, and synchronization tasks in sequential circuits.

H2: Key Features and Benefits

– Four independent bistable latches in one IC for compact design

– TTL-compatible logic for easy integration with standard logic families

– Level-sensitive latch behavior: inputs pass to outputs while enable is active, then data is latched when enable is removed

– Fast switching performance and stable operation for reliable timing

– 14-pin DIP package that is breadboard-friendly and easy to use in prototypes

H3: Why use the 7475 Latch IC?

– Simplifies temporary data storage and buffering in digital designs

– Useful in building registers, counters, and small memory elements

– Helps with control and synchronization between digital subsystems

– Great for educational labs and logic circuit experiments

H2: How the Level-Sensitive Latch Works

The 7475 operates as a level-sensitive latch. When the enable input is active, data present at each latch input is transferred to the corresponding output. Once the enable signal is removed, the outputs retain the last input state until the next enable cycle. This behavior allows precise capture and hold of digital data without continuous input updates.

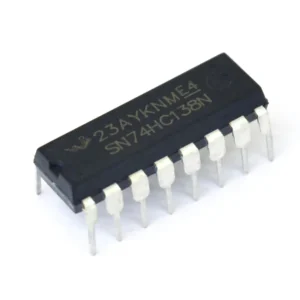

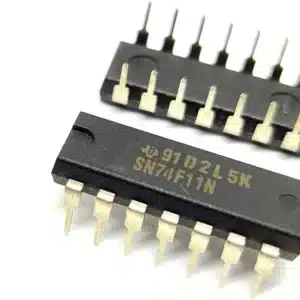

H2: Package, Pinout and Prototyping

– Standard 14-pin Dual In-line Package (DIP) for easy handling and breadboard mounting

– Breadboard-friendly form factor makes the device well suited for prototyping and educational use

– Compatible with other members of the 74xx TTL logic family for flexible system design

H2: Typical Applications

– Temporary data storage and buffering in digital circuits

– Registers and counters in sequential logic designs

– Memory elements within state machines and control logic

– Control, synchronization, and interfacing between subsystems

– Educational projects, labs, and hobbyist logic experiments

H2: Integration Tips

– Pair with other TTL family ICs for seamless logic-level compatibility

– Use proper enable timing to ensure reliable data capture

– Consider board layout and bypassing practices when integrating into larger systems

Note: Images are for Illustration Purposes Only

Reviews

There are no reviews yet