Overview

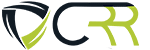

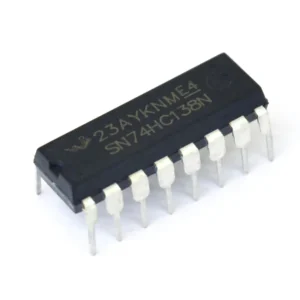

The 7473 JK Flip-Flop IC is a dual, high-performance JK bistable multivibrator from the 74xx TTL logic family. Each of the two independent JK flip-flops includes J, K, clock (CLK) and asynchronous clear (CLR) inputs plus complementary Q and Q̅ outputs. Packaged in a standard DIP-14 format, the 7473 is perfect for prototyping on breadboards, development circuits and integration into custom PCBs for both education and professional digital designs.

Key Features

- Two independent JK flip-flops in a single DIP-14 package

- Edge triggered operation for precise timing control

- Each flip-flop provides J, K, CLK and CLR inputs and Q, Q̅ outputs

- Supports Set, Reset, Toggle and Hold operations

- TTL-compatible inputs and outputs for easy interfacing with 74xx logic

- High-speed switching with low power consumption

- Typical operating voltage: 5V (4.75V to 5.25V)

Specifications

- IC Number: 7473

- Logic Type: Dual JK Flip-Flop (bistable multivibrator)

- Flip-Flops per Package: 2

- Inputs per Flip-Flop: J, K, CLK, CLR

- Outputs per Flip-Flop: Q, Q̅ (complementary outputs)

- Operating Voltage (Vcc): 4.75V to 5.25V (typical 5V)

- Propagation Delay (tPD): 20 ns (typical)

- Input Current (High): 40 μA (max)

- Input Current (Low): -1.6 mA (max)

- Output Current (Low): 16 mA (max)

- Output Current (High): -0.4 mA (typical)

- Package Type: DIP-14 (Dual Inline Package)

- Operating Temperature Range: 0°C to +70°C

Typical Applications

- Frequency division and digital counters

- Sequential logic circuits and state machines

- Data storage, registers and small memory units

- Timing, control systems and pulse shaping

- Signal toggling in sensor and timing circuits

- Educational labs and prototyping

Pin Configuration and Functional Notes

Each flip-flop has four primary inputs: J, K, CLK and CLR. The CLK input is edge triggered to ensure reliable state changes on the intended clock transition. CLR is asynchronous and resets the flip-flop regardless of the clock. Q and Q̅ provide true and complementary outputs for downstream logic.

Design Tips

- Use proper decoupling (0.1 μF ceramic) close to Vcc and GND to minimize switching noise.

- Avoid floating inputs; tie unused inputs to defined logic levels through resistors if needed.

- Observe fan-out limits when driving multiple TTL inputs from a single output.

- For reliable operation at higher speeds, keep signal traces short and minimize capacitance on clock lines.

Why Choose the 7473 JK Flip-Flop IC

The 7473 offers a reliable, TTL-compatible dual JK solution for a wide range of sequential logic tasks. Its DIP-14 package makes it easy to use in breadboard prototyping and educational projects while providing the speed and stability required for production designs such as counters, frequency dividers and small memory elements.

Note: Images are for illustration purposes only.

Reviews

There are no reviews yet